Smart Transformer Hardware, Power Converter Control and Reliability

Approved by

| About Report                                                                       |                                      |  |  |  |  |  |  |

|------------------------------------------------------------------------------------|--------------------------------------|--|--|--|--|--|--|

| Report Title : Smart Transformer Hardware, Power Converter Control and Reliability |                                      |  |  |  |  |  |  |

| Report Status                                                                      | : Final                              |  |  |  |  |  |  |

| Project Reference                                                                  | : LV Engine                          |  |  |  |  |  |  |

| Date                                                                               | : 15/11/2018                         |  |  |  |  |  |  |

|                                                                                    | Report Progress                      |  |  |  |  |  |  |

| Created by                                                                         | : Markus Andersen, Giovanni De Carne |  |  |  |  |  |  |

| Reviewed by                                                                        | : Marco Liserre, Ali Kazerooni       |  |  |  |  |  |  |

: Michael Eves

#### Disclaimer

This report has been prepared as part of the LV Engine project, a globally innovative project to demonstrate the functionalities of a Smart Transformer, funded by Ofgem through the Network Innovation Competition mechanism. All learnings, outcomes, models, findings information, methodologies or processes described in this report have been presented on the information available to the project team at the time of publishing. It is at the discernment and risk of the reader to rely upon any learnings outcomes, findings, information, methodologies or processes described in this report.

Neither SPEN, nor any person acting on its behalf, makes any warranty, representation, undertaking or assurance express or implied, with respect to the use of any learnings, outcomes, models, information, method or process disclosed in this document or that such use may not infringe the rights of any third party. No responsibility or liability is or will be accepted by SPEN, or any person acting on its behalf, including but not limited to any liabilities with respect to the use of, or for damage resulting in any way from the use of, any learnings, outcomes, models, information, apparatus, method or process disclosed in the document.

## Contents

| Glossary of Terms                                                                                                                                                                    | 6      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Executive Summary                                                                                                                                                                    | 8      |

| List of figures                                                                                                                                                                      | 11     |

| 1. Introduction to the LV Engine project                                                                                                                                             | 14     |

| 1.1. Background                                                                                                                                                                      | 14     |

| 1.2. Report scope and objectives                                                                                                                                                     | 14     |

| 1.3. Report structure                                                                                                                                                                | 15     |

| 2. Hardware for the Smart Transformer                                                                                                                                                | 16     |

| 2.1. From line-frequency transformer to the Smart Transformer                                                                                                                        | 16     |

| 2.2. ST architectures classification                                                                                                                                                 |        |

| 2.3. ST topologies for the different power conversion stages                                                                                                                         | 21     |

| 2.4. Integration of a bipolar LVDC-grid                                                                                                                                              |        |

| 2.5. Literature review on possible ST architectures and evaluation of potential services                                                                                             | 25     |

| 2.6. Impact of ST architecture on estimated costs                                                                                                                                    |        |

| <ul> <li>2.7. Selection of suitable components for the converter stages</li></ul>                                                                                                    | 35<br> |

| 2.8. Sizing of the power semiconductors                                                                                                                                              |        |

| <ul><li>2.8.1. Impact of the junction temperature on maximum power semiconductor current</li><li>2.8.2 Impact of grid conditions on the sizing of the power semiconductors</li></ul> |        |

| 2.8.3. Impact of fault currents on system design                                                                                                                                     |        |

| 3. Software for the Smart Transformer                                                                                                                                                | 61     |

| <ul> <li>3.1. Controller design</li></ul>                                                                                                                                            |        |

| 3.2. Controller implementation                                                                                                                                                       | 84     |

Take care of the environment. Printed in black and white and only if necessary.

#### Smart Transformers, Hardware, Software and reliability

| 3.2.1. Centralized controller                                              |    |

|----------------------------------------------------------------------------|----|

| 3.2.2. Decentralized controller                                            |    |

| 3.2.3. Implementation of centralized and de-centralized control capability |    |

| 3.2.4. Transition between LFT fed grid and ST fed grid                     | 91 |

| 3.3. Possible communication interfaces                                     | 92 |

| 4. Reliability considerations                                              |    |

| 4.1. Definition of reliability and introduction of availability            |    |

| 4.2. Reliability of the ST                                                 |    |

| 4.2.1. System level impact of the ST failure                               |    |

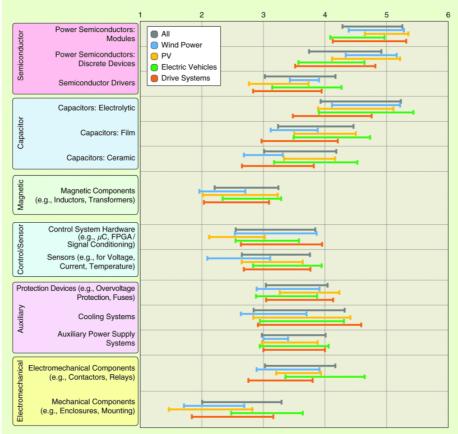

| 4.2.2. Reliability of components in power converters                       |    |

| 4.2.3. Reliability of power semiconductors                                 |    |

| 4.2.4. Reliability of capacitors                                           |    |

| 4.2.5. Failure of the cooling system                                       |    |

| 4.2.6. Interaction of the ST's component with the ambient conditions       |    |

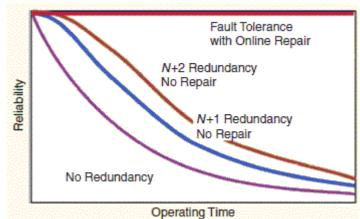

| 4.3. Modularity impact on the reliability                                  |    |

| 4.4. Innovative solution for reliability enhancement                       |    |

| 4.4.1. Condition monitoring                                                |    |

| 4.4.2. Power semiconductors                                                |    |

| 4.4.3. DC-link capacitors                                                  |    |

| 4.5. Operation and Maintenance concepts                                    |    |

| 4.6. Environmental impact of the ST                                        |    |

| 4.7. Safety requirements for STACOM application                            |    |

| 5. Key findings and recommendations                                        |    |

| 5.1. Findings and recommendations for the hardware                         |    |

| 5.2. Findings and recommendations for the software                         |    |

| 5.3. Findings and recommendations for the reliability                      |    |

| 6. Conclusions                                                             |    |

| 7. References                                                              |    |

## **Glossary of Terms**

| Abbreviation | Definition                                        |  |  |  |  |  |  |  |

|--------------|---------------------------------------------------|--|--|--|--|--|--|--|

| AC           | Alternating Current                               |  |  |  |  |  |  |  |

| ADC          | Analog to Digital Conversion                      |  |  |  |  |  |  |  |

| AI           | Aluminium                                         |  |  |  |  |  |  |  |

| B2B          | Back-to-Back                                      |  |  |  |  |  |  |  |

| CC           | Current Control                                   |  |  |  |  |  |  |  |

| CHB          | Cascaded H-Bridge                                 |  |  |  |  |  |  |  |

| CSPI         | Cooling System Performance Index                  |  |  |  |  |  |  |  |

| DAB          | Dual Active Bridge                                |  |  |  |  |  |  |  |

| DBC          | Direct Bonded Copper                              |  |  |  |  |  |  |  |

| DC           | Direct Current                                    |  |  |  |  |  |  |  |

| DPC          | Direct Power Control                              |  |  |  |  |  |  |  |

| DSL          | Digital Subscriber Line                           |  |  |  |  |  |  |  |

| DSOGI        | Dual Second Order Generalized Integration         |  |  |  |  |  |  |  |

| DSP          | Digital Signal Processors                         |  |  |  |  |  |  |  |

| dsrfPLL      | Decouple Double Synchronous Reference Frame PLL   |  |  |  |  |  |  |  |

| EMI          | Electromagnetic Interface                         |  |  |  |  |  |  |  |

| EMIF         | External Memory Interface                         |  |  |  |  |  |  |  |

| ESR          | Equivalent Series Resistance                      |  |  |  |  |  |  |  |

| FDP          | Failure Distribution Function                     |  |  |  |  |  |  |  |

| FIFO         | First-In-First-Out                                |  |  |  |  |  |  |  |

| FLL          | Frequency Locked Loop                             |  |  |  |  |  |  |  |

| FPD          | Frequency Phase Detector                          |  |  |  |  |  |  |  |

| FPGA         | Field Programmable Gate Array                     |  |  |  |  |  |  |  |

| GaN          | Galium Nitride                                    |  |  |  |  |  |  |  |

| HT           | Hybrid Transformer                                |  |  |  |  |  |  |  |

| IC           | Integrated Circuit                                |  |  |  |  |  |  |  |

| IGBT         | Insulated Gate Bipolar Transistor                 |  |  |  |  |  |  |  |

| LASJ         | Large Area Solder Joint                           |  |  |  |  |  |  |  |

| LF           | Loop Filter                                       |  |  |  |  |  |  |  |

| LFT          | Line-Frequency Transformer                        |  |  |  |  |  |  |  |

| LV           | Low Voltage                                       |  |  |  |  |  |  |  |

| MAC          | Multiple Active Bridge                            |  |  |  |  |  |  |  |

| MLCC         | Multilayer Ceramic Capacitor                      |  |  |  |  |  |  |  |

| MMC          | Modular Multilevel Converter                      |  |  |  |  |  |  |  |

| MOSFET       | Metal-Oxide-Semiconductor Field-Effect Transistor |  |  |  |  |  |  |  |

| MPPF         | Metallized Polypropylene Film                     |  |  |  |  |  |  |  |

| MV           | Medium Voltage                                    |  |  |  |  |  |  |  |

| NOP          | Normal open point                                 |  |  |  |  |  |  |  |

| NPC          | Neutral Point Clamped                             |  |  |  |  |  |  |  |

| OCT          | Onload Tap Changer                                |  |  |  |  |  |  |  |

| PCI          | Peripheral Component Interconnected               |  |  |  |  |  |  |  |

| PD           | Phase Detector                                    |  |  |  |  |  |  |  |

| PI           | Proportional Integral                             |  |  |  |  |  |  |  |

| PLC          | Power Line Communication                          |  |  |  |  |  |  |  |

| PLL          | Phase Locked Loop                                 |  |  |  |  |  |  |  |

| PoF          | Physics of Failure                                |  |  |  |  |  |  |  |

| PR           | Proportional Resonant                             |  |  |  |  |  |  |  |

| PV           | Photovoltaic                                      |  |  |  |  |  |  |  |

| PWM          | Pulse Width Modulation                            |  |  |  |  |  |  |  |

| Q            | Reactive power                                    |  |  |  |  |  |  |  |

| QSG          | Quadrature Signal Generator                       |  |  |  |  |  |  |  |

|              |                                                   |  |  |  |  |  |  |  |

| RMS     | Root Means Square                    |  |  |  |  |  |  |

|---------|--------------------------------------|--|--|--|--|--|--|

| Si      | Silicon                              |  |  |  |  |  |  |

| SiC     | Silicon Carbide                      |  |  |  |  |  |  |

| SOGI    | Second Order Generalized Integration |  |  |  |  |  |  |

| SPWM    | Sinusoidal Pulse Width Modulation    |  |  |  |  |  |  |

| SRC     | Series Resonance Converter           |  |  |  |  |  |  |

| SRF     | Synchronous Reference Frame          |  |  |  |  |  |  |

| SST     | Solid State Transformer              |  |  |  |  |  |  |

| ST      | Smart Transformer                    |  |  |  |  |  |  |

| STATCOM | Static Synchronous Compensator       |  |  |  |  |  |  |

| THD     | Total Harmonic Distortion            |  |  |  |  |  |  |

| TR      | Transformer                          |  |  |  |  |  |  |

| uPP     | Universal Parallel Port              |  |  |  |  |  |  |

| VC      | Voltage Control                      |  |  |  |  |  |  |

| VCO     | Voltage Controller Oscillator        |  |  |  |  |  |  |

| VOC     | Voltage Oriented Control             |  |  |  |  |  |  |

| VSC     | Voltage Source Converter             |  |  |  |  |  |  |

| WBG     | Wide Band Gap                        |  |  |  |  |  |  |

#### Executive Summary

This report builds on the previous academic works and also a fresh literature review to identify key hardware, software and reliability requirements for a Smart Transformer (ST). The findings of this report, where they are deemed to be appropriate, will be used for development of Smart Transformer technical specification and also informing the product design as part of LV Engine project. SP Energy Networks (SPEN) is delivering LV Engine project funded by Ofgem which aims to install Smart Transformers within power distribution secondary substations (11/0.4kV) with the goal to provide voltage control capability, active/reactive power control capability and dc-connectivity. For the tendering of the ST, this report provides key recommendations, which are mandatory for the ST to provide the desired functionality in the different trial sides.

The report is separated in three subsections, which are addressing the following contents:

- (1) **Hardware for the ST:** Review of potential ST designs by means of their power converter architectures, topologies, power semiconductor technology, the required devices and definition of hardware requirements

- (2) **Software for the ST:** Review of software by means of controller design and communication for the power electronics of the ST

- (3) **Reliability for the ST:** Review on reliability challenges and reliability requirements for the ST

In the following, the main contents are separated by the subsections and the main findings are summarized. The first subsection, addressing the **hardware for the ST**, includes the following contents and findings:

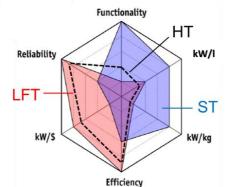

- The On Load Tap Changer (OLTC) and hybrid transformer are discussed as potential alternatives to the ST. A qualitative comparison with the ST is made in terms of functionality, power density, reliability, efficiency and costs.

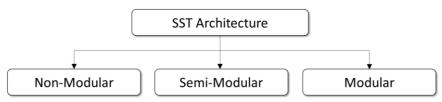

- A comprehensive review on ST architectures is provided and the architectures are grouped in dependence of the number of power stages (single-stage, two-stages, and three-stages) and the modularity level (non-modular, semi-modular and modular). The characteristics of each configuration are investigated with respective advantages and disadvantages in terms of independent control of MV and LV grid, harmonic filtering capability and DC connectivity.

- The architectures are grouped in dependence of the number of power conversion stages and the modularity. The applicability of the architectures in the LV Engine schemes is evaluated by means of the capability to provide grid services, such as DC connectivity, power flow control, harmonic filtering and reactive power control.

- The hardware costs of different topologies are qualitatively estimated by consideration of the number of power semiconductors, filter requirements and software design effort.

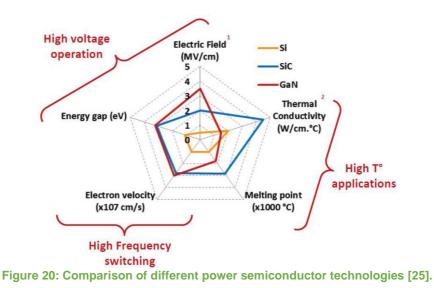

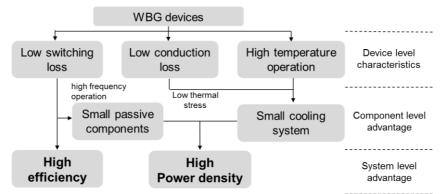

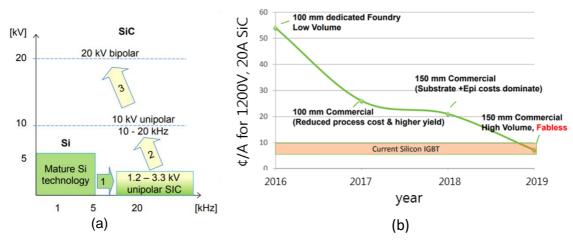

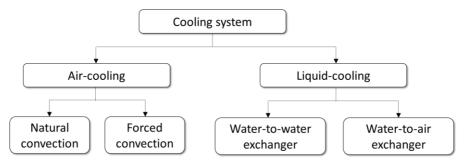

- The selection of major components (power semiconductor technology, cooling system and medium frequency transformer) and its impact on the system is examined. For the power semiconductor technology, the advantages and disadvantages of wide band gap devices are elaborated and compared with Si-devices in terms of efficiency, switching frequency, robustness, technology maturity and costs. Furthermore, the impact of each technology on the different power stages is evaluated and recommendations for the application of suitable technology for each power conversion stage are made. For the cooling system, the characteristics of air-cooling and liquid-cooling systems are presented and compared in

terms of cooling system performance. For the medium frequency transformer, the core materials are examined as well as the impact of the dielectric stress for the transformer.

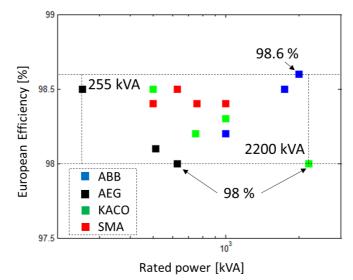

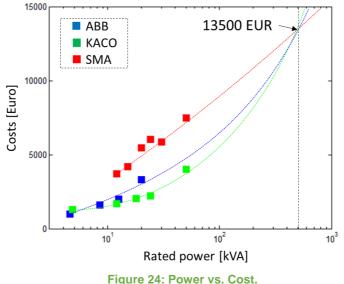

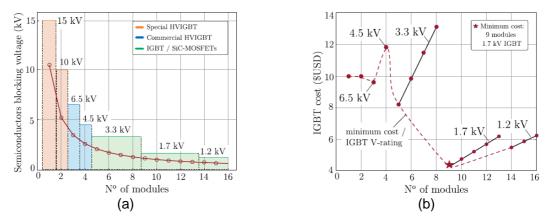

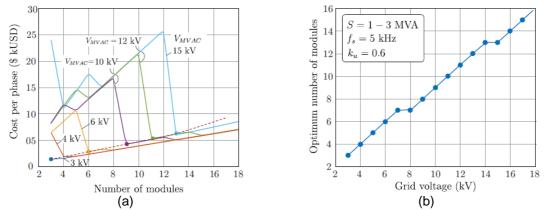

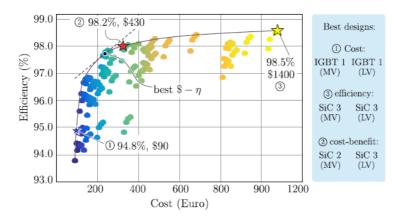

- The costs and efficiency of LV and MV side converters are estimated by benchmarking commercial power converters: PV converters for the LV side and commercially available MV converters for MV side. Furthermore, for the DC/DC stage in the three-stage configuration, the impact of the number of building blocks on the costs and the efficiency is discussed. The results provide criteria for the specification of the ST requirements.

- The sizing of the power semiconductors is analysed for the different operation modes of the ST and the permitted disturbances for which the ST has to stay grid-connected. The design requirements for the power semiconductors in terms of their voltage and current ratings is provided. Additionally, the impact of fuses in the feeders and the required fault current is discussed.

The section addressing **software for the ST** contains the following contents and findings:

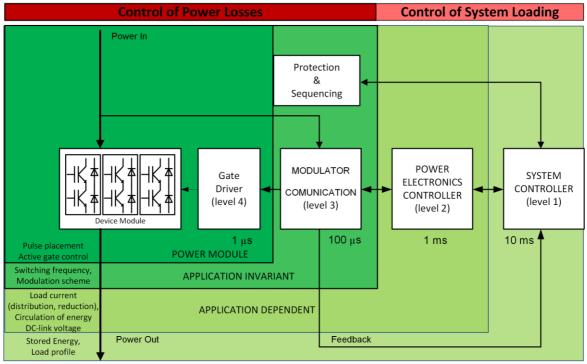

- Control requirements for each power stage considering different ST architectures (singlestage, two-stage and three-stage configurations) are addressed. The control objective of the LV side converter is determined in accordance with the LV Engine schemes.

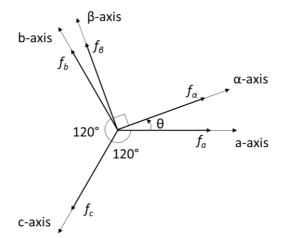

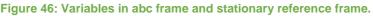

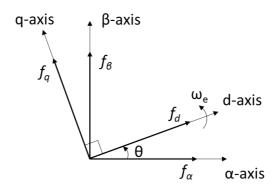

- The ST controller design in different reference frames (stationary and rotating) is discussed. Furthermore, the two required control modes (grid forming and grid feeding) are examined. As a resulting challenge, the transition between the two control modes is highlighted and a solution is proposed.

- The grid synchronization is addressed and the importance to select a suitable algorithm is highlighted. Various Phase Locke Loop (PLL) schemes are reviewed and their control performance (static and dynamic) is compared.

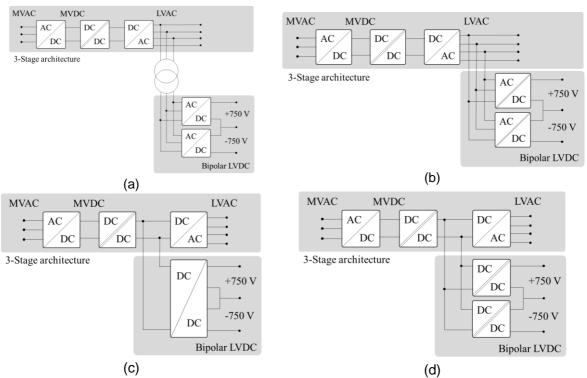

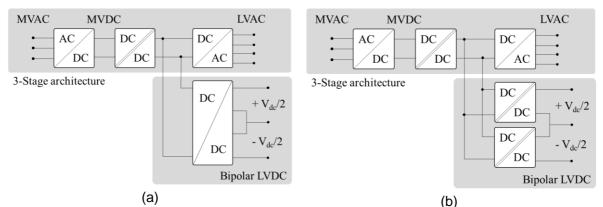

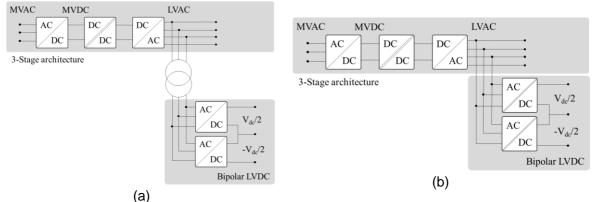

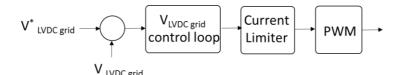

- The capability to connect DC-grids to the ST is examined, showing possible architectures with either DC/DC or AC/DC converters. Here, the considered DC-grid features a bipolar LVDC (±750 V) grid.

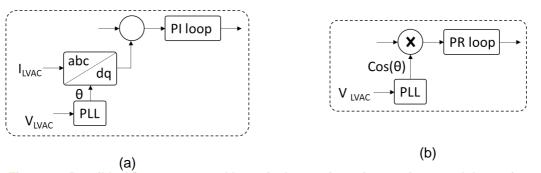

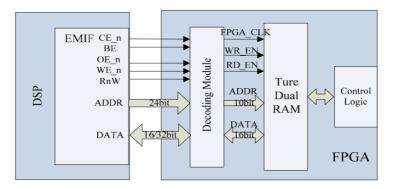

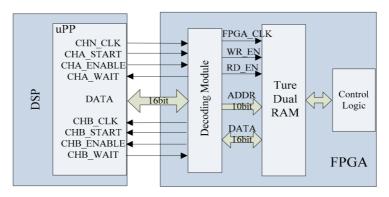

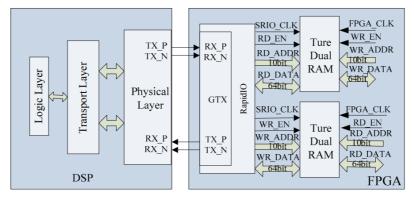

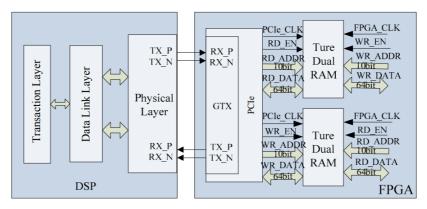

- The implementation of the control algorithm is addressed from the control hardware point of view, considering DSPs and FPGAs. The features of each device are presented and a hybrid solution is described considering the communication interfaces between them.

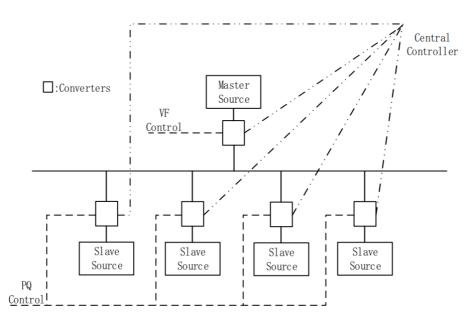

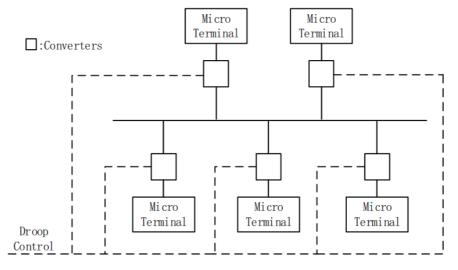

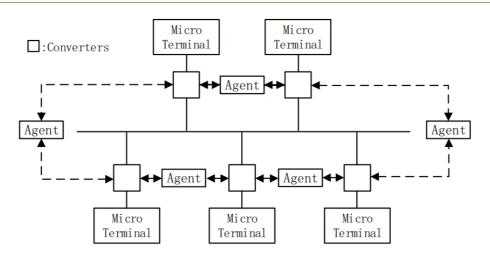

- The features of the centralized control, decentralized control and multi-agent based control are considered and the implementation of different control loops in different centralized/decentralized units is recommended.

- Possible communication interfaces of a ST-fed grid are addressed considering the date rate and the communication distance.

The section addressing the **reliability of the ST** contains the following contents and findings:

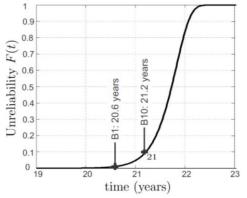

- Reliability and availability definition along with a discussion about the use of a constant failure rate for reliability evaluation

- Analysis of the impact of a fault on the system operation in the different LV-engine schemes.

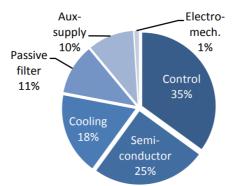

- Identification of the expected most sensitive components of the ST, which are power semiconductors, capacitors and the cooling system. Root causes for their failure are examined.

- Innovative concepts for the increase of reliability for the most sensitive components are described and the temperature is identified as a critical stressor for multiple components.

- Challenges for the humidity and the condensation in the substation of the ST are described and the impact on the components of the ST are examined.

- Operation and maintenance concepts for the ST are discussed and a report from the applications in wind turbines is used to provide recommendations to achieve high reliability.

## List of figures

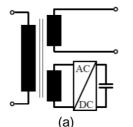

| Figure 1: Hybrid Transformer in shunt configuration: (a) Magnetic coupling and (b) Direct couplin                                       |                  |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|

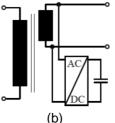

| Figure 2: Hybrid Transformer in series configuration: (a) Magnetic coupling and (b) Direct couplin                                      |                  |

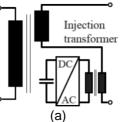

| Figure 3: Combined configuration: (a) Magnetic coupling and (b) Direct coupling.                                                        |                  |

| Figure 4: Comparison of LFT, HT and ST performance characteristics                                                                      |                  |

| Figure 5: ST architecture classification in dependence of the number of power stage                                                     |                  |

| Figure 6: Example of (a) 1 stage, (b) 2 stages and (c) 3 stages configurations                                                          | 19               |

| Figure 7: ST architecture classification in accordance with the modularity                                                              |                  |

| Figure 8: Example of (a) non-modular, (b) semi-modular (shown only DC-DC stage) and (c) mod concept (shown only DC-DC stage).           |                  |

| Figure 9: Example for MV stage converter in the 3 stages configuration; (a) Neutral Point Clamp                                         |                  |

| (NPC), (b) Cascaded H-Bridge (CHB) and (c) Modular Multilevel Converter (MMC)                                                           |                  |

| Figure 10: Example for DC/DC stage converter in the 3 stages configuration; (a) Series Resonar                                          |                  |

| Converter (SRC), (b) Dual Active Bridge (DAB) and (c) Multiple Active Bridge (MAB)                                                      |                  |

| Figure 11: Example for LV stage converter in the 3 stages configuration; (a) 2-Level, (b) NPC an                                        |                  |

| T-type 4-wire Voltage Source Inverter (VSI)                                                                                             |                  |

| Figure 12: Three-stage architecture with a bipolar LVDC connectivity; by (a) non-isolated AC/DC                                         |                  |

| isolated AC/DC, (c) non-isolated DC/DC and (d) isolated DC/DC.                                                                          | , (D)<br>24      |

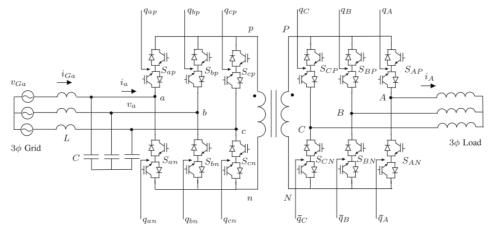

| Figure 13: 1-stage configuration by University of Minnesota: (MVAC) Matrix -(TR)-Matrix (LVAC)                                          | [10]             |

|                                                                                                                                         |                  |

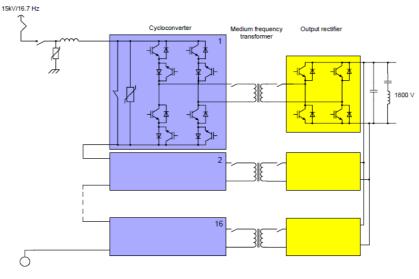

| Figure 14: 2-stage configuration by (a) ABB [11], (b) University of Alberta [12]: (MVAC) Matrix-(T Rectifier (LVDC).                    | <sup>-</sup> R)- |

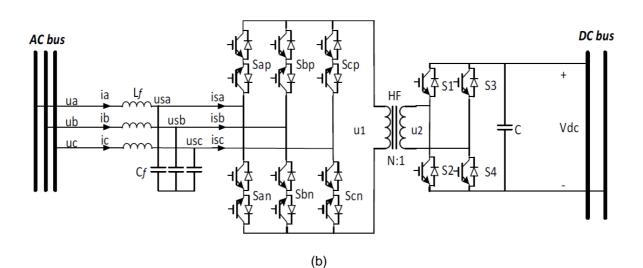

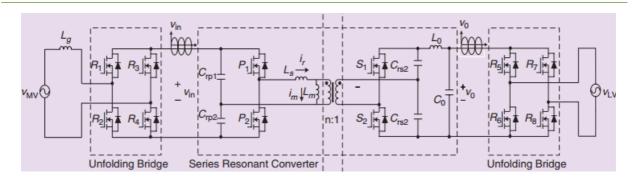

| Figure 15: 1-stage configuration by FREEDM [13]: (MVAC) Unfolding -SRC (TR)- Unfolding (LV/                                             |                  |

|                                                                                                                                         |                  |

| Figure 16: 2-stage configuration by ETH [14]: (MVAC) Unfolding -(TR)-DC/DC (LVDC)                                                       |                  |

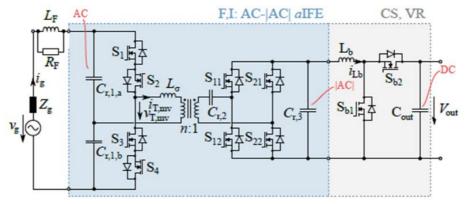

| Figure 17: 3-stage configuration: (a) (MVAC) CHB -SRC (LVDC)-(LVAC) [15],[16] ,[17](b) (MVAC)                                           | C)               |

| CHB-Semi-modular SRČ (LVDC)-(LVAC) [18] (c) (MVAC) CHB-DAB (LVDC)-(LVAC) [13] (d) (M<br>Modular-(MVDC) Cascaded SRC (LVDC)-(LVAC) [19]. | 1VAC)            |

| Modular-(MVDC) Cascaded SRC (LVDC)-(LVAC) [19].                                                                                         | 28               |

| Figure 18: (MVAC) Current source-resonance circuit-current source (LVDC) [20]                                                           |                  |

| Figure 19: Concept of a back-to-back converter based ST                                                                                 |                  |

| Figure 20: Comparison of different power semiconductor technologies [25]                                                                |                  |

| Figure 21: Advantage of the Wide Band-Gap (WBG) devices                                                                                 |                  |

| Figure 22: Prospect for (a) development and (b) price of SiC devices.                                                                   | 36               |

| Figure 23: Power vs. European efficiency Curve.                                                                                         | 40               |

| Figure 24: Power vs. Cost                                                                                                               | 40               |

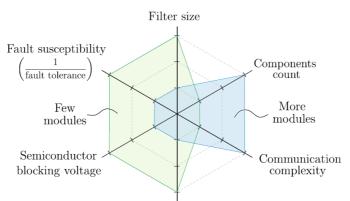

| Figure 25: Trade-offs for the selection of the number of cells/modules in a system                                                      | 42               |

| Figure 26: Influence of number of modules on (a) required semiconductor blocking voltage and (                                          |                  |

| cost (based on 2017 market price)                                                                                                       | 42               |

| Figure 27: (a) Influence of the number of modules and grid voltage on system cost per phase an                                          |                  |

| optimum number of modules in terms of cost depending on grid voltage                                                                    |                  |

| Figure 28: Trade-off between cost and efficiency for the design of a multi-winding DC/DC conver                                         |                  |

| (QAB) [27]                                                                                                                              |                  |

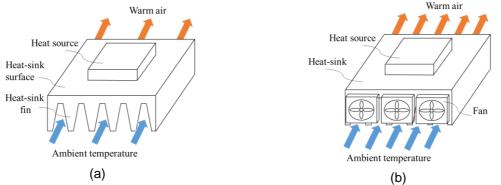

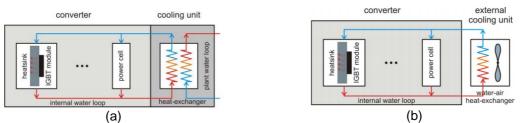

| Figure 29: Category of cooling system for power semiconductor devices.                                                                  |                  |

| Figure 30: Air-cooling system: (a) natural convection and (b) forced convection system                                                  | 44               |

| Figure 31: Liquid-cooling system: (a) liquid-to-liquid heat exchanger and (b) liquid-to-air heat                                        |                  |

| exchanger [28]                                                                                                                          |                  |

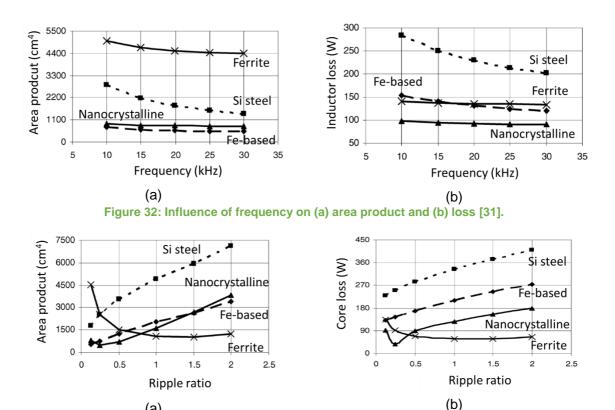

| Figure 32: Influence of frequency on (a) area product and (b) loss [31].                                                                |                  |

| Figure 33: Influence of ripple ratio (lpk-pk/ldc) on (a) area product and (b) core loss [31]                                            |                  |

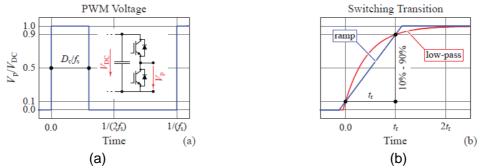

| Figure 34: PWM signal with a constant duty cycle. (b) Approximations of the switching transition:                                       |                  |

| ramp function and the step response of a first order low-pass filter [32]                                                               |                  |

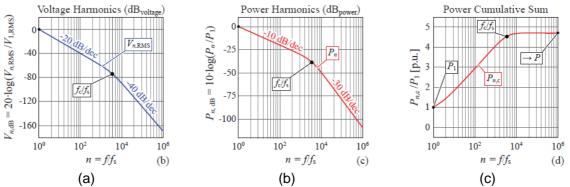

| Figure 35: Envelope of (a) the voltage harmonics, (b) the power losses harmonics and (c) cumul                                          |                  |

| sum of the power harmonics [32].                                                                                                        | 50               |

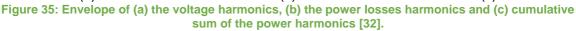

| Figure 36: Impact of (a) the switching frequency and rise time and (b) duty cycle to the dielectric [32].                               |                  |

| Figure 37: PWM voltages of (a) 2-level inverter and (b) multilevel cascaded H-bridge inverter [32                                       |                  |

Take care of the environment. Printed in black and white and only if necessary.

| Figure 38: Impact of (a) the modulation index of the fundamental component and (b) the higher                                              | 52  |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| harmonics and (a) the switching frequency on the dielectric loss [32]                                                                      |     |

| Figure 39: Three stages ST architecture.                                                                                                   | .52 |

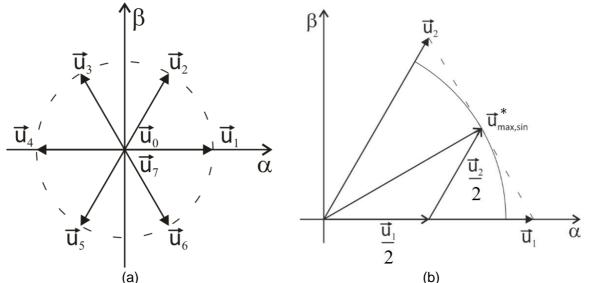

| Figure 40: (a) Space vectors of a 2 level VSC and (b) maximum sinusoidal converter output voltage the 2 level VSC.                         | .54 |

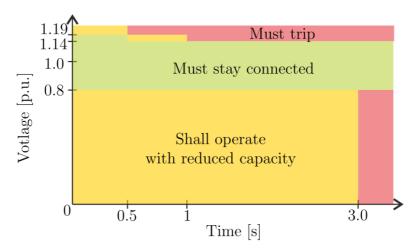

| Figure 41: Requirements for LV converters according to G99                                                                                 |     |

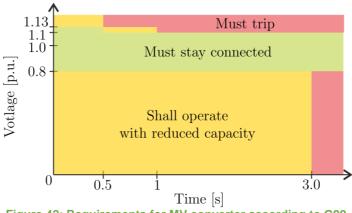

| Figure 42: Requirements for MV converter according to G99                                                                                  |     |

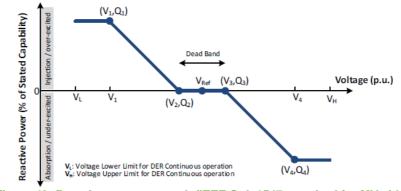

| Figure 43: Reactive power control: (IEEE Std. 1547, required for MV side)                                                                  |     |

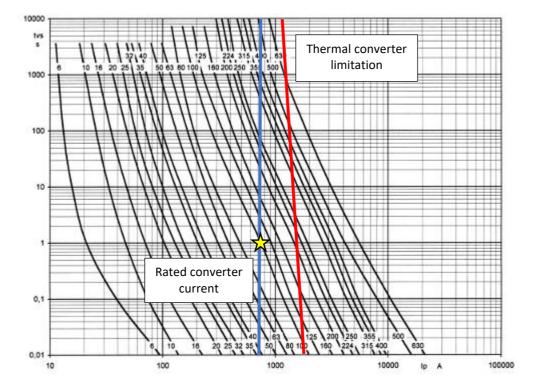

| Figure 44: Typical time-current characteristics of fuses according to IEC/EN 60269-2 with indication                                       |     |

| the rated converter current and sketched thermal converter limitation                                                                      |     |

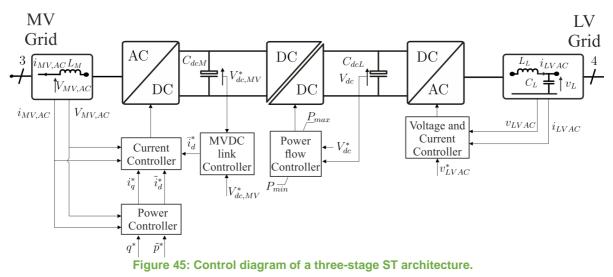

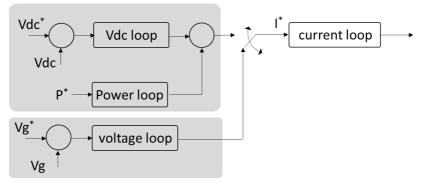

| Figure 45: Control diagram of a three-stage ST architecture                                                                                |     |

| Figure 46: Variables in abc frame and stationary reference frame.                                                                          |     |

| Figure 47: Variables in stationary reference frame and synchronous reference frame                                                         |     |

| Figure 48: Typical control block in the synchronous frame                                                                                  |     |

| Figure 49: Schematic control block in the stationary frame                                                                                 |     |

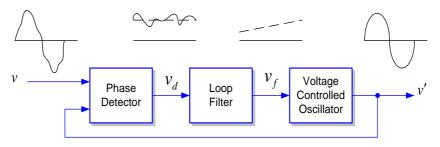

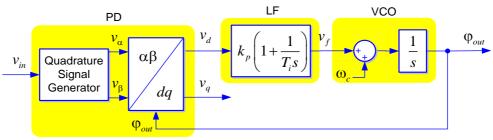

| Figure 50: Basic structure of a PLL                                                                                                        |     |

| Figure 51: Synchronous reference frame PLL [37]                                                                                            |     |

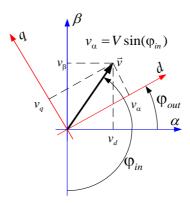

| Figure 52: Vector representation of the QSG output signals [37]                                                                            | .69 |

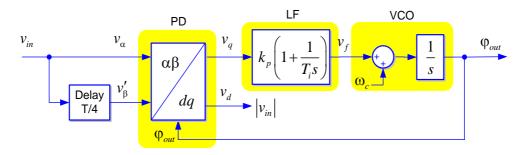

| Figure 53: PLL based on T/4 transport delay.                                                                                               |     |

| Figure 54: PLL based on the inverse coordinate transformation [37].                                                                        |     |

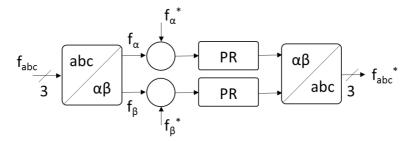

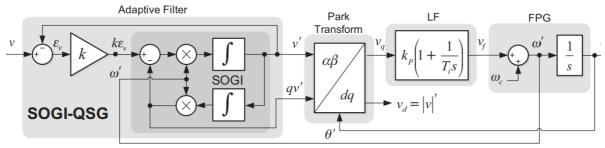

| Figure 55: Diagram of the SOGI-based PLL (SOGI-PLL) [37]                                                                                   | .71 |

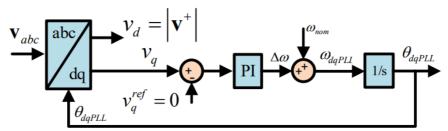

| Figure 56: SRF-PLL for three-phase system [40].                                                                                            |     |

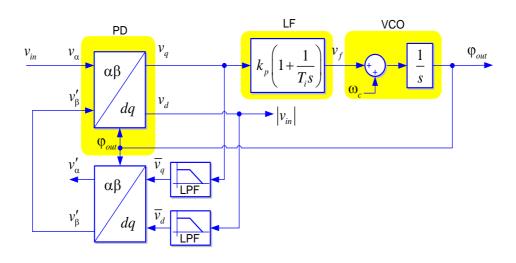

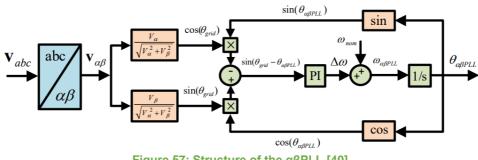

| Figure 57: Structure of the αβPLL [40].                                                                                                    |     |

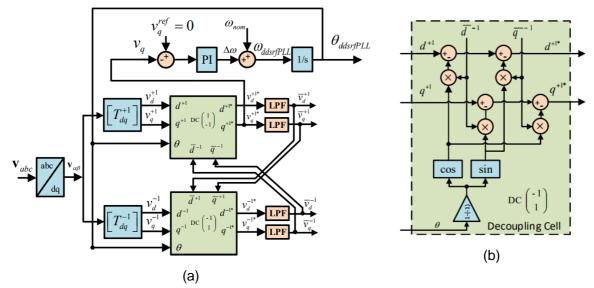

| Figure 58: (a) Block diagram of the ddsrfPLL and (b) single decoupling cell [40]                                                           |     |

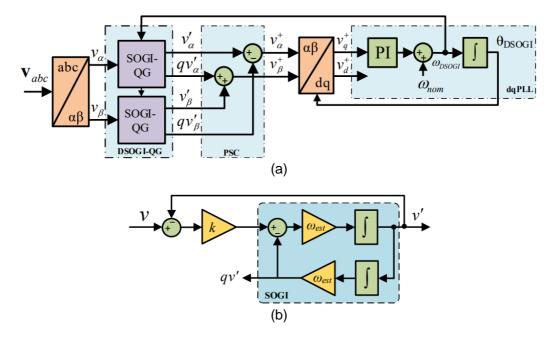

| Figure 59: (a) Block diagram of the DSOGI-PLL and (b) SOGI block diagram [40]                                                              |     |

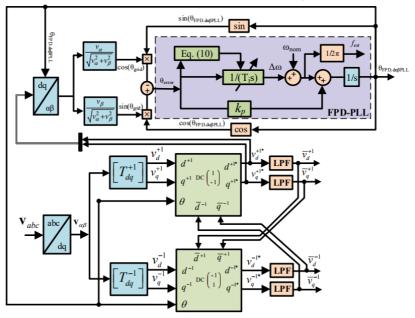

| Figure 60: Block diagram of FPD based dαβPLL                                                                                               | .76 |

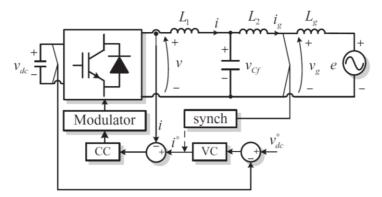

| Figure 61: Cascaded control of the DC voltage (VC) through the AC current control (CC) for grid                                            |     |

| feeding mode operation [10].                                                                                                               |     |

| Figure 62: Control block diagram with PI current control for a three wire three phase system                                               |     |

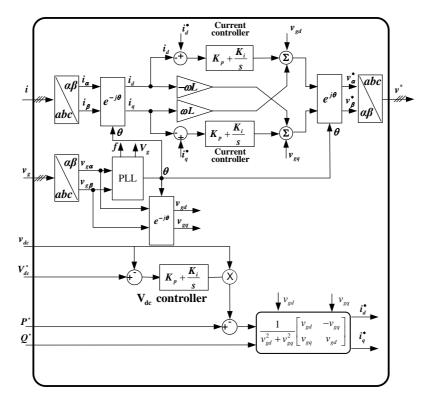

| Figure 63: Direct Power Control (DPC) without PWM modulator [10].                                                                          |     |

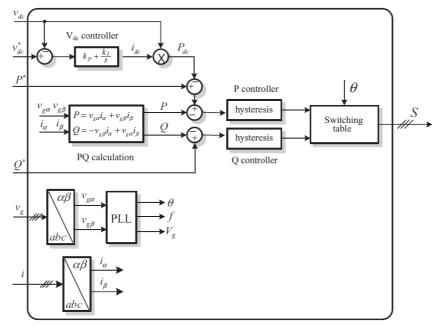

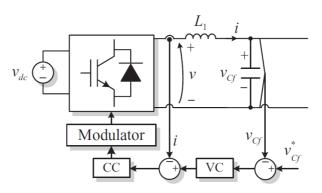

| Figure 64: AC voltage (VC) with the AC current control (CC) for grid forming mode operation [10]                                           |     |

| Figure 65: Basic configuration of control for two operation modes.                                                                         | .80 |

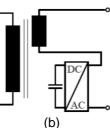

| Figure 66: Three-stage architecture with a bipolar LVDC connectivity by (a) non-isolated DC/DC                                             | ~ 1 |

| converter and (b) isolated DC/DC converter.                                                                                                | .81 |

| Figure 67: Three-stage architecture with a bipolar LVDC connectivity by (a) non-isolated AC/DC converter and (b) isolated AC/DC converter. | 01  |

| Figure 69: Control block diagram for AC/DC converter for the regulation of the DC-grid voltage                                             |     |

| Figure 68: Control block diagram for a DC/DC converter regulating the DC-grid voltage                                                      |     |

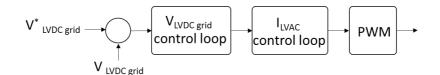

| Figure 70: Possible AC current control loops in the rotating reference frame and the stationary                                            | .02 |

| reference frame: (a) PI loop and (b) PR loop.                                                                                              | 83  |

| Figure 71: EMIF interconnect between DSP and FPGA [45].                                                                                    |     |

| Figure 72: uPP interconnect between DSP and FPGA [45]                                                                                      |     |

| Figure 73: RapidIO interconnect between DSP and FPGA [[45]                                                                                 |     |

| Figure 74: PCIe interconnect between DSP and FPGA [45]                                                                                     |     |

| Figure 75: Architecture of master-slave control as an example, where the slaves control the apparei                                        |     |

| power control and the master the voltage and the frequency [43].                                                                           |     |

| Figure 76: Architecture of peer-to-peer control [43]                                                                                       |     |

| Figure 77: Architecture of a multi-agent control system [43].                                                                              |     |

| Figure 78: Minimum data acquisition requirements defined [49].                                                                             |     |

| Figure 79: Change of the power transfer between ST and LFT during connection of the ST and                                                 | -   |

| continuous operation of the LV grid.                                                                                                       | .91 |

| Figure 80: Unreliability curve with Bx lifetime.                                                                                           |     |

| Figure 81: The critical components of power electronics systems by application in the opinion of                                           |     |

| industry experts [56].                                                                                                                     | .96 |

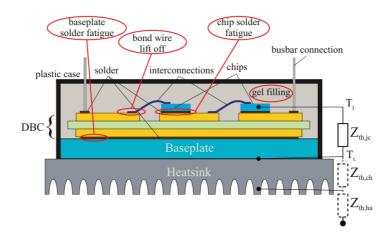

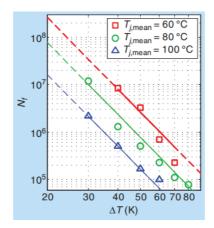

| impedances [59]9<br>Figure 83: The number of cycle to failure and the relationship between thermal swing and cycles to<br>failure [62]9                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                            |

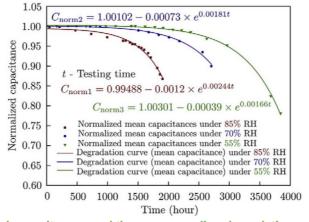

| Figure 84: Normalized capacitances and the corresponding degradation curves under different                                                                                                                                                                |

| humidity levels [73]                                                                                                                                                                                                                                       |

| Figure 85: Failures in an offshore wind power generation system [74]10                                                                                                                                                                                     |

| Figure 86: Impact of redundancy on the reliability of a system [78]10                                                                                                                                                                                      |

| Figure 87: various chances for the implementation of active thermal control in a power electronic                                                                                                                                                          |

| system [83]                                                                                                                                                                                                                                                |

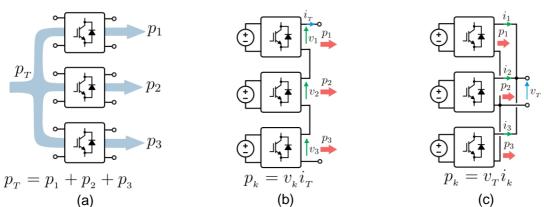

| Figure 88: (a) power routing concept in a modular system. (b) Series connection of building blocks, where the voltage is used to control the power and (c) parallel connection of the building blocks, where the current is used to control the power [84] |

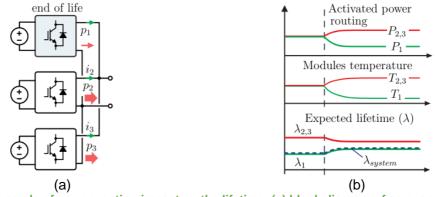

| Figure 89: Example of power routing impact on the lifetime: (a) block diagram of an example system highlighting one module is close to the end of life, (b) expected lifetime graphic showing the impact of the power routing on the system's lifetime.    |

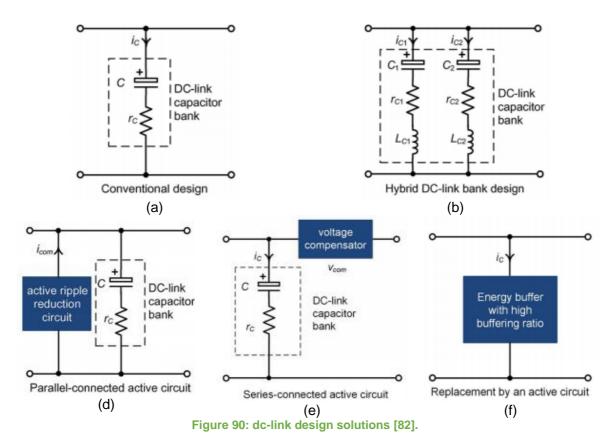

| Figure 90: dc-link design solutions [82]                                                                                                                                                                                                                   |

## **1. Introduction to the LV Engine project**

## 1.1. Background

SP Energy Networks initiated the LV Engine project with the goal to support the transition to a low carbon economy in Great Britain [1]. The key objective of the project is to design and trail the deployment of Smart Transformers (ST)s in the distribution grid within secondary substations (11/0.4kV) for ensuring a sufficient hosting capacity of the electrical network for renewable energy sources and electric vehicle charging stations. In contrast to the conventional transformer, which is a passive device, the ST enables to provide voltage control, power flow control and dc-grid connectivity. The employment of the ST will be trailed in five LV Engine schemes, whereas three of them address the installation in a pure AC-grid and the other two target the connection of DC-grids.

The installation of Smart Transformers in the electrical distribution grid requires interdisciplinary cooperation in the fields of power system, power electronics and communications. With respect to medium voltage connectivity and potentially employed medium frequency transformers, there is a lack of industrial products and designs need to be evaluated carefully, whether they can provide the desired functionalities. Moreover, the interaction of power electronics with the grid and its protection results in an interaction, which needs to be considered during the design procedure. Thereby, the interaction between hardware and software also impacts the resulting requirements for the rating of the hardware.

Power converters are commonly applied for the grid-connection in renewable energy sources or Static Synchronous Compensators (STATCOM)s. However, in the LV Engine project, the power electronics need to act in voltage control mode (for radial networks) and in power control model (for meshed networks), which challenges the control and the communication of the ST. Moreover, the reliability of the ST is of major importance to provide a high quality of service to the customers in the distribution grid. Therefore, the reliability of the ST requires to be set to very high standards already in the design and redundancy needs to be considered to increase the reliability.

This technical report investigates suitable hardware for the ST, software for the ST and reliability challenges for the ST. It concludes recommendations for the design of the ST.

## 1.2. Report scope and objectives

The goal of this report is to support the tendering for the ST hardware and software specifications within the scope of the LV Engine project. In additions, it is the goal to inform potential manufactures about possible design solutions. This includes:

- Understanding which power converters are suitable in the scope of the LV Engine schemes and which ones will not be capable to fulfil the specifications of the projects

- Analyse different components and technologies for the ST and to evaluate their impact on the functionality and the performance of the ST

- Analyse the required control and communication, which is required to provide the desired functionality of the ST

- Identify challenges in the controller design and the communication of the ST

- Identify reliability challenges and provide potential solutions to overcome them

For meeting these objectives, a comprehensive literature review is made and solutions for ST applications and an evaluation is performed. Moreover, solutions from other power electronics applications are selected and those solutions are considered for ST applications.

## 1.3. Report structure

The report is structured as follows:

- Section 2 addresses the hardware of the ST

- Section 3 addresses the software of the ST

- Section 4 addresses the reliability of the ST

- Section 5 identifies key findings and recommendations

- Section 6 provides conclusions.

## 2. Hardware for the Smart Transformer

## 2.1. From line-frequency transformer to the Smart Transformer

In the following subsection, a short introduction to the ST is provided. The conventional transformer and potential other solutions for increasing the controllability in the grid are introduced and their potential functionality is described.

The conventional Line-frequency Transformer (LFT) is the key element of electrical distribution grids. It provides galvanic isolation and adapts voltage levels for energy transmission. However, it is a passive element and does not provide any controllability, which is desired in certain conditions. To enable voltage adaption of the LFT, the Onload Tap Changer (OTC) has been developed and enables changing the voltage with discrete step sizes. However, to the current state, the dynamics of the OTC are very limited and the phase angle between input voltage and output voltage is fixed.

For extending the controllability, the Hybrid Transformer (HT) has been proposed [2, 3]. The HT is a combination of LFT with a power converter, which has been proposed to enhance the limited functionalities of the LFT with an OTC. Technically, this approach exploits the inherent characteristic of the power converters, which facilitates the control of different electrical parameters and therefore ancillary grid services. The potential configurations of HTs are briefly described in the following.

#### Hybrid Transformer in shunt configuration

The power converter for AC-DC conversion is connected in parallel with the LFT as shown in **Figure 1**, which is the so-called Static Synchronous Compensator (STATCOM). It enables to inject reactive current into the grid and therefore the grid voltage and the power factor can be controlled. The functionality of active filtering to eliminate harmonics in the grid can be provided.

#### Hybrid Transformer in series configuration (Field upgradeable transformer) [4]

As shown in **Figure 2**, the power converter can be connected in series on the low voltage side or the medium voltage side. Therefore, it enables manipulating the grid voltage and the power factor. Similar to the shunt configuration, it can act as an active harmonic filter.

Figure 1: Hybrid Transformer in shunt configuration: (a) Magnetic coupling and (b) Direct coupling.

Figure 2: Hybrid Transformer in series configuration: (a) Magnetic coupling and (b) Direct coupling.

Figure 3: Combined configuration: (a) Magnetic coupling and (b) Direct coupling.

#### Hybrid Transformer in shunt and series configuration [5]

The combined configuration consists of a shunt and a series configuration, which is connected to the same DC-link as a back-to-back converter. The configurations are shown in Figure 3.

Unlike the configurations presented before, active and reactive voltage/current can be supported by the power converter.

#### Concept of the Smart Transformer

In traction application, the potential volume and weight reduction have encouraged developments for the substitution of the LFT with a medium frequency transformer fed by power semiconductors. The resulting system is referred to as Solid State Transformer (SST). The SST is transferring the overall power, which differentiates it from the HT. In the SST application, the volume and weight reduction are the main driver of the technology. However, the SST in Smart grid applications is not motivated by the volume and weight, but the control and communication capability, which makes the SST smart and therefore, it is referred to as Smart Transformer (ST). It is a series element in the grid and enables decoupling of the connected AC grids to a certain extent. In grid forming operation, the ST is able to control the grid voltage and the grid frequency – independently from the other AC and DC grids potentially connected to the ST.

Figure 4: Comparison of LFT, HT and ST performance characteristics.

#### Comparison of Hybrid Transformer, low frequency transformer and Smart Transformer

The HT concept enables to enhance the controllability of the LFT with the partly rated power converter. The ST instead is solution for replacing the LFT and providing full controllability of the grid, whereas it needs to be rated for the full power. The controllability and the rated power of the HT are typically 10-20% with respect to the rating of the ST [6]. Apart from the controllability, the performance in terms of weight, volume, costs and efficiency is essential and needs to be considered. As an extension of [6], the four characteristics are compared for the ST, the LFT and the HT in Figure 4. Here, it should be noted that only material cost is considered, implying that a labour costs, software and profits are not taken into account. In the weight and volume calculation, DC-link capacitors, power semiconductors, heatsink, filter inductors, transformer, electronics and cabinet/frame are considered. For the evaluation of the losses, the filter inductors and power semiconductors are considered. The ST has a significantly lower volume in comparison to the LFT, whereas the material cost and losses are increased to 460 % and 280 %, respectively [6]. The major contribution to the weight and volume of the ST are the passive filter components. Hence, the filter design is of particular interest. The emerging technologies such as Silicon Carbide (SiC) can be used to realize the higher switching frequency and consequently enable reducing volume and weight of the passive components. In addition, the efficiency can be improved by using wide band gap devices with their lower losses.

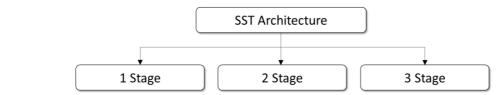

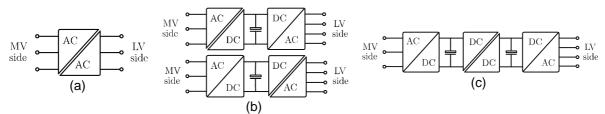

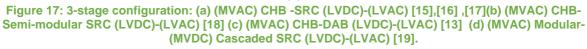

## 2.2. ST architectures classification

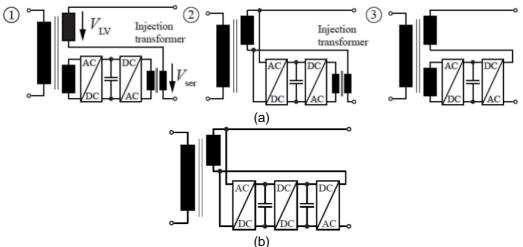

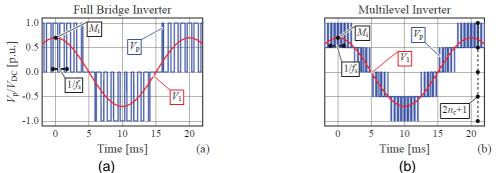

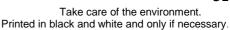

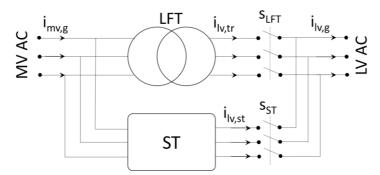

Several power converter architectures with applicability to the ST have been proposed in literature. In the following they are grouped in order to provide the fundamentals for their comparison. As pointed out before, the ST is encouraged by the capability to provide grid services. These grid services are strongly correlated to the number of DC links and power conversation stages. Therefore, the ST architectures are grouped in dependence of the number of power conversion stages as shown in **Figure 5**: the single stage for direct conversion between MVAC-LVAC, two stages for MVAC-LVDC-LVAC and three stages for MVAC-MVDC-LVDC-LVAC. A representation of the architectures is shown in **Figure 6**. In the following, the advantages and disadvantages are discussed.

As a requirement for the system, a storage element, such as a DC link, is essential for decoupling the connected grids of the ST. With the availability of the storage element, the converter architecture may provide the following features:

- Independent generation of the voltage in the grid (MV and LV)

- Harmonic filtering capability

- DC- connectivity for DC-links (e.g. for EV charging stations or battery storage)

Single stage configuration:

Figure 5: ST architecture classification in dependence of the number of power stage.

Figure 6: Example of (a) 1 stage, (b) 2 stages and (c) 3 stages configurations.

The single power stage concept (as shown in **Figure 6 (a)**) is based on the direct power conversion between MVAC and LVAC, providing galvanic isolation. This can be achieved with matrix converter topologies, which do not require bulky DC-link capacitors. In addition, with only a single power conversion stage, the configuration of the whole system can be simple and a low number of power semiconductors is required. For the single stage ST architectures, not even DC-link capacitors are required. Consequently, the single power conversion stage may result in high power density at low cost. However, due to the lack of DC-links the MV and LV grids are strongly coupled by the energy flow, similar to the conventional line-frequency transformer. Therefore, a disturbance on one side of the grid will also be seen on the other side of the grid. An independent control of the grid voltage in the MV and LV grid is not possible. This is of high importance if services are provided and the ST needs to inject reactive power in one side of the grid or compensate current harmonics/voltage harmonics in the grid. Automatically, the other grid will be affected and potentially see a higher distortion. Therefore, matrix converters are not practical to provide grid services, because of the strong coupling of the grids.

#### Two stages configuration:

Two-stages ST architectures (as shown in **Figure 6 (b)**) can be designed with a high flexibility and in literature voltage source converter based architectures, current source converter based architectures and a mixture of both architectures have been proposed. Voltage source converter based architectures use capacitors for energy storage, whereas current source converters use inductors for the storage of energy. Both enable to provide services and to not have limitations with respect to their applicability in the LV Engine schemes. However, voltage source converters are mostly used in commercial products. Potential reasons for the preference of voltage source converter source converter are doubts about the performance of current source converters (e.g. losses and common mode voltages) and the security in case of emergency shut down. As an additional objection for current source converters, power semiconductors with inverse voltage blocking capability are required.

In the two stages architecture with voltage source converters, the galvanic isolation is implemented either in the MV- or the LV-side. Depending on the implementation of the isolation stage, one of DC-link is available (i.e. with the MV-side galvanic isolation the LVDC grid is provided, whereas the MVDC is available when the LV-side is adopting the galvanic isolation) [7]. Depending on the adopted topology for the two stages, the grid services may be limited. However, with one DC-link in the system, the grids can be decoupled and services can be provided for most of the architectures.

As a point to consider carefully, the galvanic isolation may be provided by a medium frequency transformer or a low frequency transformer. In the latter case, there will not be the benefit in terms of weight and volume reduction of the ST.

A current source converter based architecture with two power conversion stages and no DC-links has been also proposed [8]. The drawbacks of currents source converters have been already highlighted.

#### Three stages configuration:

The three-stage ST architectures (as shown in **Figure 6 (c)**) are based on the galvanic isolation by means of the MVDC to LVDC stage, which provides certain flexibly to adopt topologies for each stage. Hence, there is a possibility to provide both MVDC and LVDC connectivity and the MVAC

and LVAC grids can be decoupled [9]. Furthermore, all grid services such as reactive power

compensation, bidirectional power flow, renewable energy and energy storage system integration, can be provided. However, a higher number of power semiconductors and capacitors are needed for this architecture and therefore the costs for the system may be higher - despite the use of devices rated for low voltage.

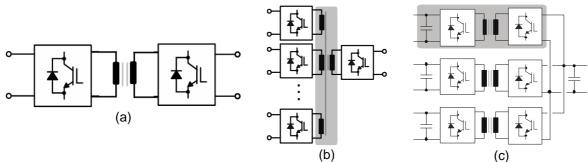

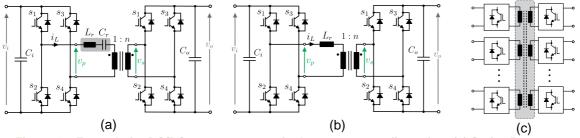

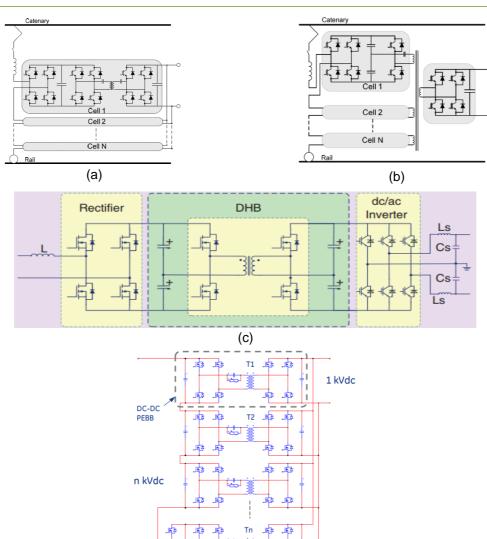

As a second level of classification, the 3 stages configuration is divided into three categories as shown in **Figure 7**: non-modular, semi-modular and modular. For each of these concepts, an example for the isolation stage is shown in **Figure 8**.

Figure 7: ST architecture classification in accordance with the modularity.

Figure 8: Example of (a) non-modular, (b) semi-modular (shown only DC-DC stage) and (c) modular concept (shown only DC-DC stage).

#### Non-modular:

Non-modular architectures require a lower number of power devices, but a high voltage blocking capability of power devices for the MV-side. Unfortunately, for Si-based devices high switching losses are associated with high blocking voltages and to our best knowledge devices with a sufficient high blocking voltage for the ST application are not commercially available at this point (IGBTs for blocking voltages higher than 6.5 kV). Furthermore, big output filters are required, fault

tolerance schemes are not available and scalability in power and voltage is not possible. As an example for this topology, the single-phase Dual Active Bridge (DAB) is shown in **Figure 8 (a)**.

#### Semi-modular:

The semi-modular concept is only applicable in the converter stage in which the isolation is realised, because it holds a transformer with multiple windings. This is not present in the other converter stages. Multi-winding medium/high frequency transformers are used for a single cell, which enables to reduce the number of transformers. In the application with high input/output voltage ratio, it enables to use devices rated for lower voltage, because several power converter cells are connected to a same transformer. As an example, the multi-winding structure is shown in **Figure 8 (b)**.

#### Modular:

The modularity concept is based on the use of several building blocks, which are connected in parallel and/or in series. Modular power converters commonly enable to adopt fault tolerant schemes and scalability in power/voltage. Because of the modularity, a higher number of components, such as transformer cores and power devices is needed. As an example for modular DC/DC converters, several series-input-parallel-output connected dual active bridges are shown in **Figure 8 (c)**.

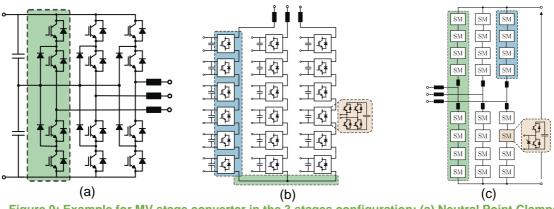

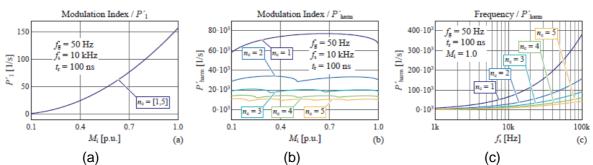

### 2.3. ST topologies for the different power conversion stages

In this section, typical building blocks for power converters in a three stages ST are presented. First, typical converter structures for the stages of a three stages architecture are presented. Remarkably, the medium voltage stage topology and the isolation stage are coupled in many architectures, whereas the low voltage stage can be chosen independently.

For the MV stage converter, multi-level topologies are usually chosen, because of the potential advantages of optimizing the design trade-offs in consideration of:

- 1) reduced dv/dt (EMI noises),

- 2) reduced filter size,

- 3) higher efficiency,

- 4) lower blocking voltage of power devices.

The multi-level topologies as an example are shown in **Figure 9**, where Neutral Point Clamped (NPC) in **Figure 9 (a)**, Cascaded H-bridge (CHB) in **Figure 9 (b)** and Modular Multilevel Converter (MMC) in **Figure 9 (c)**.

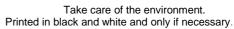

The galvanic isolation is essentially required in the isolation stage, where a medium/high frequency transformer is used. Hence, the size/weight of the passive components can be reduced, compared with the transformer designed for the line-frequency. Moreover, a higher efficiency can be achieved by reducing the switching losses with soft-switching power converter topologies. The Series Resonance Converter (SRC) as shown in **Figure 10 (a)** does not require a closed loop control, but the input and output ports are strongly coupled. This means a disturbance in one DC-link directly affect the other DC-link, even if a certain dynamic behaviour needs to be considered. The DAB, shown in **Figure 10 (b)**, and the Multiple Active Bridge (MAB), shown in **Figure 10 (c)**, need to be controlled instead. Therefore, both ports can be decoupled, whereby the MAB is consisting of a single multi-winding transformer. Consequently, the number of the passive components is reduced components is associated with the number of H-Bridges adopted in the LV-side of the MAB. In this topology, the multi-winding transformer is of high importance and it its failure interrupts the operation of all connected H-bridges. Therefore, it is recommended to select a sufficiently low number of H-Bridges.

Considering the development of the efficiency of high frequency transformers, the DAB topology is taken as an example. Its trend of increasing efficiency is shown in Table 1, where three references from literature are compared. As it can be seen, the efficiency has been increasing up to maximum 98.8 % with Wide BandGap (WBG) devices of SiC-MOSFET and the core material of

FINEMET for the transformer. Furthermore, the use of WBG devices operated with a higher switching frequency enables the use of smaller passive components.

For the LV stage converter, a 4-wire configuration is employed and connected in parallel for high current capability. Similar to the MV side converter, the multi-level topologies, which are shown in **Figure 11 (b)** and **(c)** are beneficial for reducing dv/dt and passive components with a higher efficiency, although the 2-level topology in **Figure 11 (a)** is well known and established.

Figure 10: Example for DC/DC stage converter in the 3 stages configuration; (a) Series Resonance Converter (SRC), (b) Dual Active Bridge (DAB) and (c) Multiple Active Bridge (MAB).

Figure 11: Example for LV stage converter in the 3 stages configuration; (a) 2-Level, (b) NPC and (c) Ttype 4-wire Voltage Source Inverter (VSI).

| Year                                    | 1992<br>(by M.H.Kheraluwala) | 2007<br>(by S. Inoue)             | 2016<br>(by H.Akagi)          |

|-----------------------------------------|------------------------------|-----------------------------------|-------------------------------|

| Power device                            | Plannar-Gate Si-IGBT         | Trench-Gate Si-IGBT               | Trench-Gate SiC-<br>MOSFET    |

| Rated power @ fsw                       | 50 kW @ 50 kHz               | 10 kW @ 20 kHz                    | 100 kW @ 20 kHz               |

| Medium/high<br>frequency<br>transformer | Ferrite                      | FINEMET                           | FINEMET                       |

| Efficiency @ power                      | <90%                         | 96.8 % @ 10 kW<br>97.4 % @ 3.8 kW | 98 % @ 100 kW<br>98.8 @ 41 kW |

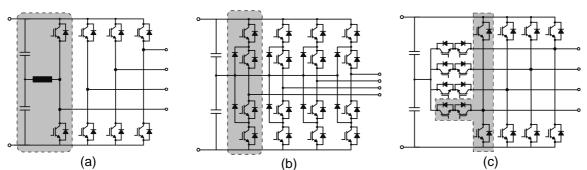

## 2.4. Integration of a bipolar LVDC-grid

The connection of an LVDC grid can be made with a direct power conversion from either the MVAC grid or the LVAC grid in a single power conversion stage. Alternatively, the grid can be connected to a DC-link of the ST. In the latter case, the ST can control the power flow between all grids and enables to isolate disturbances in the grid in which they are occurring. For the LVDC grid, the ability to provide bidirectional power flow is essential, because energy storage systems, distributed generation systems (like PV converters) and electric vehicle charging stations may be connected to it.

For the design of the LVDC grid, the authors of this work have found a lack of applicable norms with respect to voltage level, isolation requirements and protection systems. Therefore, it is required to take into account the requirements of the LVDC operator and the connected loads. This may require galvanic isolation of the DC grid, but is not absolutely mandatory. As an example, EV charging stations are required to provide galvanic isolation to the cars and therefore, the grid may not be isolated. If other DC loads are connected, which are not galvanically isolated, it is likely that the grid needs to be isolated.

As another open point, the grid voltage of the LVDC grid needs to be defined. Generally, there are conflicting goals for the optimization of the system. The maximization of the DC-grid voltage is desired for the purpose of increasing the line capacity, whereas a reduction of the grid voltage brings advantages for safety and potentially efficiency. As an example for a grid with an AC voltage of 400 V, the expected LVDC-link voltage should be in the range of 700...800 V. Thereby, the maximum LV-voltage for the grid is 1.5 kV and brings the maximum grid capacity, but a voltage transfer ratio of 2 is expected to result in lower efficiency than a unity voltage transfer ratio. The

Figure 12: Three-stage architecture with a bipolar LVDC connectivity; by (a) non-isolated AC/DC, (b) isolated AC/DC, (c) non-isolated DC/DC and (d) isolated DC/DC.

LVDC grid can be realized as a unipolar system (positive potential, neutral) and a bipolar system (positive potential, neutral, negative potential). The advantage of the bipolar concept is its natural fault tolerant property and the use of devices with half the blocking voltage with respect to the overall DC-grid voltage. The topologies, which can potentially be used to provide the DC-grid are similar to those ones introduced for the isolation stage of the ST. The bipolar LVDC grid is considered to visualize the different opportunities to realize the LVDC grid as it is shown in **Figure 12**.

The possible architectures can be categorized by the connection to AC or DC and by galvanic isolation of the converter or a non-isolated converter. In Figure 12 (a), the configuration with the non-isolated AC/DC converter is shown, whereas Figure 12 (b) shows the isolated converter. In Figure 12 (c), the converter is fed non-isolated from the DC-link and in Figure 12 (d), the converter is isolated from the DC-link.

As discussed before, the galvanic isolation may be required to prevent unwanted current flow due to grid faults between the LVAC and LVDC grid. For this purpose, the isolation may to be required, but it limits the efficiency and the power density if a low frequency transformer is adopted (as shown in **Figure 12 (a)**). The efficiency can be improved by adopting the solution shown in **Figure 12 (b)** However, a critical shortcoming of the AC/DC configurations is that the LVDC grid is highly coupled with the LVAC grid. For example, if a fault occurs in the LVAC side and the LVAC grid is shut down, the LVDC is consequently disabled.

The use of a DC/DC converter connected to the LVDC-link of the converter solves the problem of the coupled grids. This is shown in **Figure 12 (c)** and **(d)**.

## 2.5. Literature review on possible ST architectures and evaluation of potential services

The application of a power electronics based transformer as the interface between medium voltage and low voltage has been proposed in traction applications, where it was mostly referred to as

"Solid state transformer" or "Power Electronics Based Transformer". Several companies have proposed architectures and designed systems, which are introduced and discussed in the

following. A matrix converter based architecture is shown in Figure 13. It is based on a single

power conversion stage, which does not provide DC-connectivity and therefore, it may be limited in decoupling the grids. However, it is capable to provide grid services such as the reverse power flow and the reactive power support. A challenge of matrix converters in general is a complex combination of the switching states. If Sinusoidal Pulse Width Modulation (SPWM) is used, there is a limitation in the maximum modulation index, which can be used (up to 87%). This is limiting the utilization of the hardware. Another challenge is the protection in case of an immediate turn off because of the lack of a freewheeling path for the current. In comparison with other topologies, the transformer is fed by hard switching power semiconductors on the low voltage side, which limits to achieve a higher efficiency. Another challenge, which the authors of the proposed topology identify are the limitation of common mode voltages [10].

Another possibility to realize matrix converters is to use two stages with an additional DC-link as shown in Figure 14. Figure 14 (a) shows the system proposed by ABB with series connected building blocks on the MV-side and parallel connected H-bridges on the low voltage side. The medium voltage side is referred to as a cycloconverter and synthesizes its output waveform without a DC-link. The system operates similar to a matrix converter, but provides DC-connectivity and thereby the AC grids can be decoupled. As a challenge of this topology, the trade-off between limited power semiconductor losses and high frequency for the transformer needs to be determined. In Figure 14 (b) an architecture is realized with a single building block (without modularity).

A single power conversion stage based ST architecture, which is expected to achieve high efficiency is the unfolding bridge based topology shown in Error! Reference source not found.. The u nfolding bridges operate with the fundamental frequency and a medium frequency transformer, a series resonant converter in this case, is providing galvanic isolation and transfers the power. In this architecture, the unfolding bridge is on both AC-sides, whereas it is also possible to apply it only on one of the two AC-sides.

Figure 13: 1-stage configuration by University of Minnesota: (MVAC) Matrix -(TR)-Matrix (LVAC) [10].

(a)

Figure 14: 2-stage configuration by (a) ABB [11], (b) University of Alberta [12]: (MVAC) Matrix-(TR)-Rectifier (LVDC).

山

Ø,

Figure 15: 1-stage configuration by FREEDM [13]: (MVAC) Unfolding -SRC (TR)- Unfolding (LVAC).

Figure 16: 2-stage configuration by ETH [14]: (MVAC) Unfolding -(TR)-DC/DC (LVDC).

In **Figure 16**, the unfolding bridge is only applied in the medium voltage side and DC-connectivity is provided in the low voltage side. This architecture has the advantage of simplicity on the medium voltage side, whereas the low voltage side is complex to be controlled. Remarkably, in the medium voltage side, the resonant tank ( $L_F$  and  $C_r$ ) is used to achieve soft switching for the whole operation range. However, since the pulsating current has a higher amplitude, power devices with a higher rated current are required and the efficiency is worse in the high power operating range due to higher conduction losses.

Modular three-stage converter architectures are shown in **Figure 17**. The advantage of those architectures is the modularity on the cell level and potentially inherent redundancy. In addition, it is possible to independently choose the topology for the stages and to have the full controllability for grid services. As another advantage, two DC-links are separating the AC-grids, which is expected to provide improved decoupling of the two grids. The disadvantage of these topologies is a high switch count and the need for DC-links with a high capacitance.

1:1 (d)

山

æ

Figure 19: Concept of a back-to-back converter based ST.

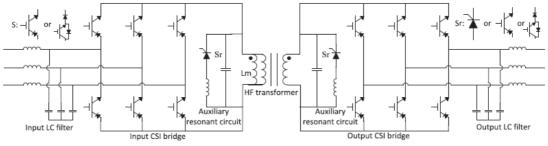

Another opportunity to realize an ST is to use current fed topologies as shown in **Figure 18**. This does not provide DC-connectivity, but it does not require DC-link capacitors. Instead, the energy is stored magnetically (inductors). As shown in the figure, auxiliary circuits are required for soft switching. It does not affect inrush currents, but the transformer size is expect to be 50% bigger than in a DAB for the same power. The topology enables to provide grid services and bidirectional power flow.

# Table 2: Comparison between three stages ST and back-to-back converter with transformer: + superior/good performance, 0 neutral, - worse/inferior performance.

|                       | Back-to-back with transformer | Three stages ST         |

|-----------------------|-------------------------------|-------------------------|

| Size and weight       | -                             | +                       |

| Functionality         | +                             | +                       |

| Efficiency            | 0                             | 0                       |

| Development costs     | +                             | -                       |

| Material costs        | +                             | -                       |

| Disturbance rejection | 0                             | +                       |

| DC-link access        | 0<br>Only LV possible         | +<br>LV and MV possible |

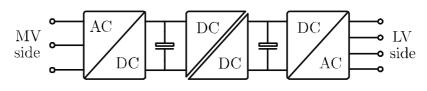

An alternative to the ST architectures without the high-frequency isolation is the use of a standard transformer and a back-to-back converter in the low voltage side as shown in Figure 19 (a). This architecture provides DC-connectivity, bidirectional power flow and grid services for both AC-grids. In comparison with a three-stage ST architecture, it is expected to be considerably less expensive, because of the existing experience for PV/wind turbine applications. A comparison between the two solutions is shown in Table 2 by means of size & weight, functionality, efficiency, development costs, material costs and disturbance rejection capability. The functionality of both solutions is similar and both architectures can perform independent voltage control in case sufficient active power is provided. For the comparison of the efficiency, a simple test case was made in a conference paper, where the ST was concluded to obtain superior efficiency in partial load operation (below 50%) [21]. However, this is comparison is highly dependent on the considered components and may change accordingly. Apart from this, the material costs and the development costs for the ST are expected to be higher. The disturbance rejection capability is referring to the decoupling capability of the two AC grids, referring to the influence of a disturbance on the other ac grid. As an example, an overvoltage or a voltage sag in one of the grids should not affect the other grid and potentially violate the voltage regulations. Therefore, it is advantageous to have more than one DC-link to limit the influence of one grid on the other grid. Consequently, the three stage solution is expected to be superior, because of the two DC-links, which are achieving a better decoupling of the grids compared to the single DC-link. The availability of the DC-links is also limited for the B2B converter with its single DC-link, whereas the SST can enable to provide MVDClink.

| Architecture                                                              | Number of<br>power<br>conversion<br>stages | Modularity<br>(system,<br>topology<br>or cell | Ľ | Applicability for<br>LV Engine<br>schemes |   | DC<br>connectivity |   | References |    |      |

|---------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------|---|-------------------------------------------|---|--------------------|---|------------|----|------|

|                                                                           | 1 2 3                                      | level)                                        | 1 | 2                                         | 3 | 4                  | 5 | ΜV         | LV |      |

| Indirect matrix converter                                                 | 1<br>(MVAC-<br>LVAC)                       | Cell,<br>system<br>level                      | x | x                                         | х | -                  | - | -          | -  | [22] |

| LF unfolding<br>bridge+current<br>source<br>SRC+LF<br>unfolding<br>bridge | 1<br>(MVAC-<br>LVAC)                       | System<br>level                               | x | x                                         | x | -                  | - | -          | -  | [13] |

| Cascaded<br>cycloconverter<br>+ 2 level VSC                               | 2<br>(MVAC-<br>LVDC-LVAC)                  | Cell,<br>system<br>level                      | x | x                                         | x | х                  | x | -          | x  | [11] |

| Isolated AC-DC<br>matrix<br>converter                                     | 2<br>(MVAC-<br>LVDC-LVAC)                  | System<br>level                               | x | x                                         | x | x                  | x | -          | х  | [12] |